基于FPGA的總線型LVDS通信系統(tǒng)設(shè)計與開發(fā)

隨著現(xiàn)代通信系統(tǒng)對高速數(shù)據(jù)傳輸需求的日益增長,F(xiàn)PGA(現(xiàn)場可編程門陣列)憑借其并行處理能力和靈活的可重構(gòu)性,在高速通信系統(tǒng)設(shè)計中發(fā)揮著關(guān)鍵作用。LVDS(低電壓差分信號)技術(shù)以其低功耗、高抗干擾性和高速傳輸特性,成為高性能通信系統(tǒng)的理想選擇。本文將探討基于FPGA的總線型LVDS通信系統(tǒng)的設(shè)計原理、關(guān)鍵模塊實現(xiàn)以及系統(tǒng)開發(fā)流程。

一、系統(tǒng)設(shè)計原理

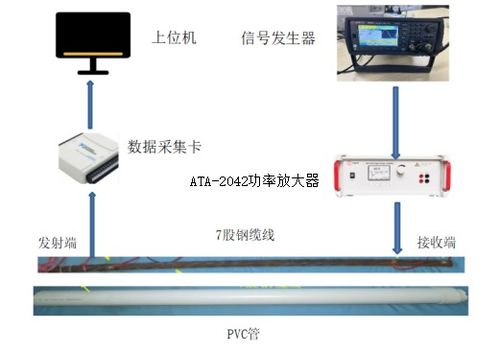

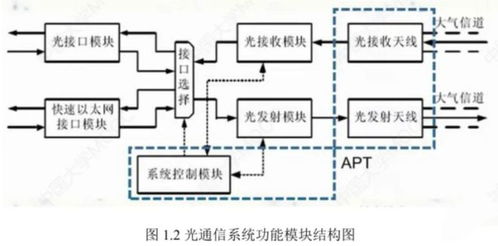

總線型LVDS通信系統(tǒng)的核心在于利用差分信號傳輸機(jī)制,通過一對互補(bǔ)的信號線來傳輸數(shù)據(jù),有效抑制共模噪聲,提升信號完整性。在FPGA平臺上,該系統(tǒng)通常包括數(shù)據(jù)發(fā)送模塊、數(shù)據(jù)接收模塊、時鐘管理模塊以及總線控制邏輯。發(fā)送端將并行數(shù)據(jù)轉(zhuǎn)換為串行LVDS信號,接收端則進(jìn)行相反的解碼過程。總線架構(gòu)允許多個設(shè)備共享同一傳輸介質(zhì),通過地址編碼和仲裁機(jī)制實現(xiàn)多節(jié)點通信。

二、關(guān)鍵模塊實現(xiàn)

- 數(shù)據(jù)編解碼模塊:基于FPGA的LVDS接口通常使用Serializer/Deserializer(SerDes)技術(shù)。發(fā)送端通過并串轉(zhuǎn)換將數(shù)據(jù)打包成LVDS信號,接收端則進(jìn)行串并轉(zhuǎn)換恢復(fù)原始數(shù)據(jù)。FPGA內(nèi)置的LVDS I/O引腳和專用SerDes硬核(如Xilinx的ISERDES/OSERDES)可大幅簡化設(shè)計。

- 時鐘與同步管理:高速LVDS通信對時鐘穩(wěn)定性要求極高。設(shè)計需采用時鐘數(shù)據(jù)恢復(fù)(CDR)技術(shù)或同步時鐘方案,確保發(fā)送與接收端的時序?qū)R。FPGA的鎖相環(huán)(PLL)和時鐘管理塊(CMT)可用于生成精確的時鐘信號。

- 總線協(xié)議與控制邏輯:實現(xiàn)基于地址的多設(shè)備通信需設(shè)計總線仲裁器、幀封裝模塊和錯誤檢測機(jī)制(如CRC校驗)。FPGA的可編程邏輯允許靈活定制協(xié)議,例如模擬I2C、SPI或自定義總線標(biāo)準(zhǔn)。

- 抗干擾與信號完整性:通過PCB布局優(yōu)化(如差分線等長布線)、終端匹配電阻以及FPGA的預(yù)加重/均衡設(shè)置,減少信號衰減和反射。

三、系統(tǒng)開發(fā)流程

- 需求分析:明確通信速率、節(jié)點數(shù)量、傳輸距離及功耗約束。例如,目標(biāo)為1 Gbps速率、10節(jié)點總線系統(tǒng)。

- 架構(gòu)設(shè)計:選擇FPGA型號(如Intel Cyclone系列或Xilinx Artix-7),規(guī)劃LVDS通道數(shù)量與總線拓?fù)浣Y(jié)構(gòu)。

- RTL編碼與仿真:使用Verilog/VHDL實現(xiàn)各模塊,并通過仿真工具(如ModelSim)驗證時序邏輯與協(xié)議正確性。

- 綜合與布局布線:利用FPGA開發(fā)工具(如Vivado或Quartus)進(jìn)行邏輯綜合,優(yōu)化資源分配與時序收斂。

- 系統(tǒng)測試:通過示波器分析LVDS信號眼圖,結(jié)合邏輯分析儀驗證數(shù)據(jù)傳輸準(zhǔn)確性。進(jìn)行溫濕度、電壓波動等環(huán)境測試以確保可靠性。

四、應(yīng)用與挑戰(zhàn)

該設(shè)計廣泛應(yīng)用于工業(yè)自動化、汽車電子及航空航天領(lǐng)域的高可靠性通信場景。未來,隨著FPGA技術(shù)的演進(jìn),集成更高速SerDes(如28 Gbps)和硬核協(xié)議棧將進(jìn)一步提升系統(tǒng)性能。開發(fā)中需注意信號完整性分析、電源噪聲抑制以及多節(jié)點同步等挑戰(zhàn),建議結(jié)合仿真與實測迭代優(yōu)化。

基于FPGA的總線型LVDS通信系統(tǒng)通過硬件并行處理與差分傳輸技術(shù)的結(jié)合,實現(xiàn)了高效、可靠的數(shù)據(jù)交換。隨著5G和物聯(lián)網(wǎng)技術(shù)的發(fā)展,此類系統(tǒng)將繼續(xù)推動高速互聯(lián)創(chuàng)新的前沿。

如若轉(zhuǎn)載,請注明出處:http://www.jy2y.cn/product/8.html

更新時間:2026-03-25 09:34:40